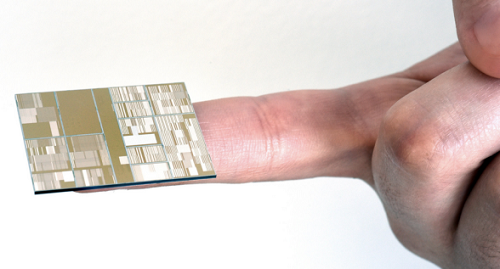

Popredná technologická spoločnosť IBM oznámila, že úspešne vyrobila čip 7nm výrobným procesom. Má nižšiu spotrebu a môže mať až 4-násobný výkon oproti súčasným čipom.

Zatiaľ čo súčasné, masovo vyrábané procesory sú vyrábané 14nm procesom a pomaly sa pripravuje prechod na 10nm výrobu, IBM má už hotový čip vyrobený 7nm FinFET procesom. Pre porovnanie – reťazec DNA má hrúbku v priemere 2,5nm.

IBM sa úspešne podarilo vyrobiť takýto čip aj vďaka použitiu zlúčeniny kremíka a germánia namiesto využitia iba čistého kremíka. Táto zlúčenina umožňuje rýchlejšie meniť tranzistorom svoj stav a taktiež spotrebuje menej energie.

Spoločnosť tvrdí, že čip vyrobený 7nm procesom by mohol byť až o polovicu menši ako čipy vyrobené 10nm procesom, pričom výkon sa zvýši minimálne o 50% pri rovnakej spotrebe. Malo by tiež byť možné vyrobiť čip s 20 miliardami tranzistorov, ktorý by poskytol až 4-násobný výkon oproti súčasným čipom.

Vyzerá to tak, že Moorov zákon sa drží zubami-nechtami. Podľa prognóz IBM bude v platnosti minimálne do roku 2018 a bude teda možné každé 2 roky zdvojnásobiť počet tranzistorov. Súčasný 7nm čip je ešte stále v štádiu vývoja a o komerčnej výrobe sa zatiaľ nehovorí. Vzhľadom na to, že ešte čakáme na 10nm čipy si na 7nm produkty počkáme asi ešte dlho.

Zdroj: techreport

Pjetro de

Shatterhand

SiliconX

Pjetro de

Shatterhand

V2